Que es chip de silicio1/9/2024

Strained silicon-which will appear in Intel's Prescott chip next year-stretches the distances between the silicon atoms in transistors, the tiny on/off switches that form the basis of a chip. The concept of strained silicon has been around for 30 years, but it only recently moved to the center of concern for chip designers.

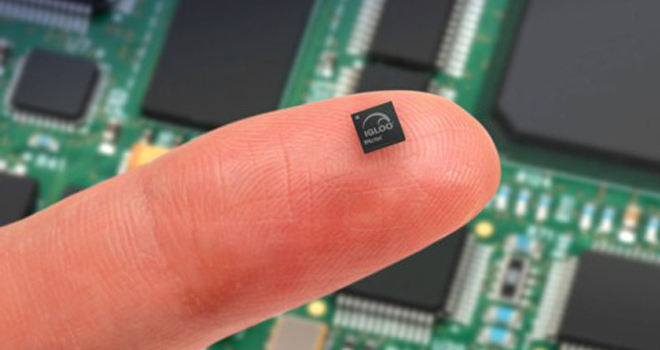

This change in perspective means that deep research in materials and transistor design-especially the kind of research that IBM and Intel researchers specialize in-will become much more important in the future. "You are going to work a hell of a lot harder to stay on a predictive curve.You are actually going to have to increase the innovation in materials." "There is a fundamental change in the methodology of progress," said Bernard Meyerson, chief technology officer of IBM's Technology group, which includes IBM Microelectronics. But this approach also leads to escalating levels of energy consumption, among other problems-spurring designers to come up with creative solutions. Typically, increasing the number of transistors (a trick accomplished by shrinking them) leads to higher performance and new capabilities for processors. Strained silicon-like double-gate and triple-gate transistors, silicon on insulator ( SOI) and other new design ideas coming to the fore-should allow chipmakers to maintain the performance curve established by Moore's Law, the semiconductor industry principle stating that manufacturers will double the number of transistors on chips every two years. The San Francisco convention, one of the principal events for semiconductor designers, will feature a keynote speech by Intel Chairman Andy Grove as well as presentations from Sony, Samsung, Pennsylvania State University and the Massachusetts Institute of Technology, among others. Researchers and design engineers from IBM and Intel will present papers at the International Electron Devices Meeting (IEDM) next week that detail their work on " strained silicon," a manufacturing technique that promises to boost processor performance by up to 20 percent. In addition, our hardware, software, and I/O adaptive SoC platform offers the flexibility and scalability of an FPGA combined with ASIC-like performance and power and the ease of use of an ASSP.The strains of creating faster processors will get an airing among chipmakers next week.

Our break-out portfolio also includes the industry's only hardware programmable homogeneous and heterogeneous 3D ICs with the highest bandwidth and system integration. The Xilinx UltraScale™ architecture delivers unprecedented levels of integration and capability while delivering ASIC-class system level performance for the most demanding applications requiring massive I/O & memory bandwidth, massive data flow, DSP, and packet processing performance. The adaptive compute acceleration platform (ACAP) Versal architecture was designed to enable all types of developers to accelerate their whole application with disruptive performance through optimized hardware and software, providing a solution that adaptable faster than the pace of silicon design cycles. Xilinx is the inventor of the FPGA, hardware adaptive SoCs, and the ACAP, designed to deliver the most dynamic processor technology in the industry. Xilinx develops highly flexible and adaptive processing platforms that enable rapid innovation across a variety of technologies-from the endpoint to the edge to the cloud.

0 Comments

Leave a Reply.AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed